A person who loves everything about electronics. I try to uncomplicate things and discover real reason behind everything we do

Friday, October 4, 2013

Temperature inversion~~cause and analysis

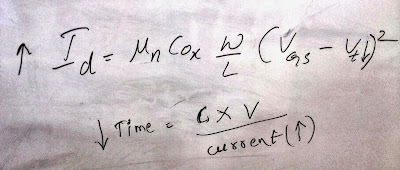

Let us first understand the basic concept of what causes the delay of the transistor from the below equation

fig 1. relation between current and delay of a mosfet

As you can find from the above that the more the current the less the delay of the PFET or NFET. Also you can refer to my previous blog on understanding the cell delay and transition.

Now you understand that cell delay depends on the current. Let us see what current depends on

Relation between mobility and current.

A phenomenon called lattice scattering happens at higher temperatures. Lattice vibrations cause the mobility to decrease with increasing temperature. Hence the resistance of a mosfet increases with increase in temperature causing current to reduce.

From the above figure we find that the current I is directly proportional to the mobility of the semiconductor. Hence as the mobility decreases, the current decreases. Hence cell delay increases.

So , temperature increases ==> cell delay increases duet to mobility

As , temperature decreases ==> cell delay should decrease due to mobility

Now this looks quite satisfying and this is normally the case without temperature inversion. Then what is causing temperature variation ? It is the Vt change..

Temperature and Vt variation

The threshold voltage of a mosfet decreases with increase in temperature as follows. Here (alpha Vt ) is a constant variable which denotes decreases in Vt as -3mv/degC.

Now observe that delay of your mosfet is basically dependent on two factors.

1. mobility due to temperature variation.

2. Vt varying with temperature

The final drain current would depend on what dominates the drain current at the given temperature. In practical when you decrease the temperature , you will be surprised to know that you will not be observing any temperature inversion. That is because there is one more factor of dependence which is supply voltage.

Cell delay and supply voltage

In the drain current equation (Vgs - Vt)squared , you observe that

1. when Vgs is high, (Vgs -Vt )amlost stays constant, hence your current is dependent on mobility

2. when Vgs is low, ( Vgs-Vt) difference dominates, hence your current is dependent on Vt

With all this happening all corners need to be addressed in the chip for successful functioning. Hence multi mode multi corners analysis is done before taping out the chips which is robust to catch all discrepancies.

Now you understand that cell delay depends on the current. Let us see what current depends on

Relation between mobility and current.

A phenomenon called lattice scattering happens at higher temperatures. Lattice vibrations cause the mobility to decrease with increasing temperature. Hence the resistance of a mosfet increases with increase in temperature causing current to reduce.

From the above figure we find that the current I is directly proportional to the mobility of the semiconductor. Hence as the mobility decreases, the current decreases. Hence cell delay increases.

So , temperature increases ==> cell delay increases duet to mobility

As , temperature decreases ==> cell delay should decrease due to mobility

Now this looks quite satisfying and this is normally the case without temperature inversion. Then what is causing temperature variation ? It is the Vt change..

Temperature and Vt variation

The threshold voltage of a mosfet decreases with increase in temperature as follows. Here (alpha Vt ) is a constant variable which denotes decreases in Vt as -3mv/degC.

Now put this in again in mosfet equation it becomes

Here we observe that Vgs - Vt term is squared which means that your current increases drastically with changes in Vt. Hence delay of your mosfet decreases drastically with change in Vt as the current increases significantly.

1. mobility due to temperature variation.

2. Vt varying with temperature

The final drain current would depend on what dominates the drain current at the given temperature. In practical when you decrease the temperature , you will be surprised to know that you will not be observing any temperature inversion. That is because there is one more factor of dependence which is supply voltage.

Cell delay and supply voltage

In the drain current equation (Vgs - Vt)squared , you observe that

1. when Vgs is high, (Vgs -Vt )amlost stays constant, hence your current is dependent on mobility

2. when Vgs is low, ( Vgs-Vt) difference dominates, hence your current is dependent on Vt

With all this happening all corners need to be addressed in the chip for successful functioning. Hence multi mode multi corners analysis is done before taping out the chips which is robust to catch all discrepancies.

Thursday, June 27, 2013

Why hold does not depend on clock frequency ?

If there is setup violation, the frequency of chip can be reduced

and we can make the chip still function. But if there is hold violation then

your chip is lost for ever. This is the most used phrase in physical design.

But did you ever try to analyse why the hold violations does not depend on the

frequency of the chip ?

First of all let us understand Setup and hold checks completely

Imagine data is travelling from FF1 to FF2 as shown in the figure.

Look at the timing diagram below

- Data1(clock cycle1 data of FF1 ) is being sampled at FF2 in clock cycle2

- Data2 (clock cycle2 data of FF1) is on its way to FF2 already

From the figure

Setup check

It says

that the data sampled from FF1 at cycle 1 should reach FF2 in cycle 2 before

FF2 setup time.

Equation

Tc2q (FF1) + Tcomb = Tclk -Tsetup

Hold check

It says that the current data ==>Data 2, which

is sampled from FF1 at cycle2, should

not arrive at FF2 at cycle2 before FF2 hold time. ( because it messes up with Data1 which is being currently captured

by FF2 in cycle2 )

In other words there Data2 from FF1 should not mess with Data1 which is already at FF2 which is currently being sampled

T.c2q (clock to Q delay of FF1) +Tcomb >= T (hold )

Your clock->Q delay and Tcomb are not at all dependent on the clock period. Hence your hold is independent of clock frequency.

Monday, May 20, 2013

Beauty of FINFET

Question ?

Why are we shifting to FinFET technology. Whats need ?

For years now the MOSFET size has been drastically decreasing so that we could cram in more and more transistors in a single piece of die to reduce the area and to improve the productivity.

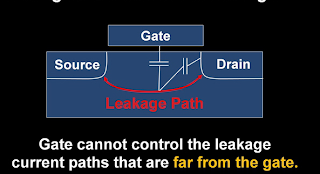

But remember everything has its own side effects. As we go on decreasing the gate length the control of gate over the channel beneath it decreases and hence the leakage current increases. This is due to a phenomena called as sub threshold current.

First let us understand what is happening inside a MOSFET through an analogy. Im mosfet the electrons flow from source drain with gate as control. The gate creates channel for the electrons to flow. It generally creates a mirror charge for the channel flow.

This can be viewed as water flowing through a pipe which is squeezed in the middle by your hand on one side ( which is here a gate) which is obstructing the water flow. Now

As the distance between drain and source decreases by decreasing the gate length, the substrate region which offers off resistance when switch is OFF in between drain and source decreases. Hence the resistance of the switch decreases, therefore more leakage current starts to flow through the switch when the switch is OFF.

Sub threshold current.

At lower nodes where the distance between drain and source reduces the conduction from source to drain is mainly due to diffusion of electrons rather than drifting of electrons. This means that the channel can never be turned off as there would always be some conduction through diffusion of electrons.

Point here to remember is that the Fin is sitting on top of substrate and the channel which is formed is completely isolated from the substrate. So obviously there would be no leakage current which flows through the substrate when the transistor is OFF unlike the planar transistor . Which means we have almost achieved a NO leakage transistor.

Point here to remember is that the Fin is sitting on top of substrate and the channel which is formed is completely isolated from the substrate. So obviously there would be no leakage current which flows through the substrate when the transistor is OFF unlike the planar transistor . Which means we have almost achieved a NO leakage transistor.

In other words, the water flowing through the pipe is being controlled on all sides by the valve which is present on all sides. So there is no leakage flowing in the down part unlike the earlier planar transistor. Hence the problem was solved intelligently.

Why are we shifting to FinFET technology. Whats need ?

For years now the MOSFET size has been drastically decreasing so that we could cram in more and more transistors in a single piece of die to reduce the area and to improve the productivity.

But remember everything has its own side effects. As we go on decreasing the gate length the control of gate over the channel beneath it decreases and hence the leakage current increases. This is due to a phenomena called as sub threshold current.

First let us understand what is happening inside a MOSFET through an analogy. Im mosfet the electrons flow from source drain with gate as control. The gate creates channel for the electrons to flow. It generally creates a mirror charge for the channel flow.

This can be viewed as water flowing through a pipe which is squeezed in the middle by your hand on one side ( which is here a gate) which is obstructing the water flow. Now

As the distance between drain and source decreases by decreasing the gate length, the substrate region which offers off resistance when switch is OFF in between drain and source decreases. Hence the resistance of the switch decreases, therefore more leakage current starts to flow through the switch when the switch is OFF.

More the distance between source and drain, more is the resistance it can offer and hence less leakage. But remember reducing gate length is required for fitting in more transistors and reducing the chip area and die size. So we are left with no option here either we have to compromise on leakage or on area.

A gate is in general like a valve which controls the flow through the channel. As you remove the channel you are closing the valve and turning off the transistor. If you have to create a channel then you should open the valve.

Why is leakage current present in standard planar MOSFET?

In standard planar transistor as the transistor sizes are decreasing the source and drain come closer. Hence there will always be some leakage current flowing through the substrate from source to drain without the influence of gate. It is called sub threshold leakage current. It happens under weaker gate voltages or when the gate is off.

At lower nodes where the distance between drain and source reduces the conduction from source to drain is mainly due to diffusion of electrons rather than drifting of electrons. This means that the channel can never be turned off as there would always be some conduction through diffusion of electrons.

Remember that the leakage path exists far away from the gate and the gate has no control over it.

"It means valve cannot control the water flow which is far away from iself. This gives rise to leakage "

This limitation can be solved with the help of

FINFET transistor

This is when the finfet technology comes with a promising feature

In FINFET transistor the gate is on three sides of the FIN. A fin is a set of drain and source cutting through the gate. Now when the transistor is on the channel gets formed on all sides ( remember in planar mosfet channel only gets formed on one side ) and heavy rush of current flows through it.

Point here to remember is that the Fin is sitting on top of substrate and the channel which is formed is completely isolated from the substrate. So obviously there would be no leakage current which flows through the substrate when the transistor is OFF unlike the planar transistor . Which means we have almost achieved a NO leakage transistor.

Point here to remember is that the Fin is sitting on top of substrate and the channel which is formed is completely isolated from the substrate. So obviously there would be no leakage current which flows through the substrate when the transistor is OFF unlike the planar transistor . Which means we have almost achieved a NO leakage transistor. In other words, the water flowing through the pipe is being controlled on all sides by the valve which is present on all sides. So there is no leakage flowing in the down part unlike the earlier planar transistor. Hence the problem was solved intelligently.

Saturday, May 4, 2013

Understanding transition

What is transition

It is the amount of time required to charge

discharge the load capacitance of a cell completely.

Every mosfet (standard

cells are made of them ) can be viewed as capacitance. A cell output capacitance is nothing but the summation of the

capacitance of all the cells connected to its output in parallel + the net

capacitances.

The time required to

switch ON or OFF the cell can be viewed as the time required to charge the

capacitance.

To understand transition in an easier way

Let us assume the

standard cell or buffer as a motor which is filling up a tank which is

analogous to capacitance. The time required to charge the capacitance is

nothing but the time required to fill the tank completely.

The bigger the tank the more is the

time required to fill the tank. Which means the more the capacitance, the more is

the transition time or the time required to charge the capacitance.

motor pumping water into a tank

What is the disadvantage of having more transition ?

A more transition would

mean the motor (standard cell ) would have to spend lot of power as it has to

switch on for a longer time. Which means we would be having more dynamic power

consumption.

Having more transition would also mean that your arrival time of data increases. Hence meeting setup gets more tougher. Let us have a look at how transition is affecting setup

Having more transition would also mean that your arrival time of data increases. Hence meeting setup gets more tougher. Let us have a look at how transition is affecting setup

How to decrease transition then?

One way to decrease transition would be to increase the power of motor

so that it could fill up the tank quickly. In practical on chip it is same as

the increasing the drive strength of the buffer so that it could charge more

capacitance quickly.

Another way to decrease transition is to reduce the capacity of the tank

that needs to be filled which is nothing but to reduce the output

capacitance. The capacitance can be reduced by inserting a buffer in the

path so that it would see only have to charge the next cell and wire

capacitance instead of seeing the previous

total high load.

It is like inserting another motor after certain length so that the

first motor would only have to fill up small tank ( capacitance reduces because

subsequent wire capacitance reduces and

load gets splitted) till the next motor and the subsequent motor would drive it

from there. Now two motors share the effort and hence time required to fill the

tank comes down.

Saturday, April 13, 2013

Understanding fingering of transistors

What is the need for fingering??

The problem is really with putting those cells or let us call instances on the rows which have a fixed height. So in that case if you would like to increase the the height of the transistor in order to have more drive strength (or to deliver more current to the load capacitance ) it is not possible. The solution would be to use the fingering technique.

Understanding fingering.

Let us understand fingering by comparing it with a real life scenario. Let us say you have a tap which draws out water. How can you make the tap pull out more water?? It is by increasing the diameter of the tap. More is the diameter more is the current that goes out.

water coming out of small pipe

increasing the diameter of pipe causes more water to flow out

Increasing the diameter of the tap is analogous to increasing the height or length of the transistor region so as to deliver more current.

Now i give a constraint that you cannot increase the diameter of the pipe to draw out more water. So what do you do to get more water???. Simple. Put more pipes in parallel so as to increase the water flow.

putting more pipes in parallel without increasing the diameter causes more water flow

This is what exactly we are doing in fingering. We keep the transistor of fixed size so that the height remains constant but then we put more number of transistors in parallel so as to deliver more current to the load.

In this case we join the sources and drains in chained fashion so that they act like taps in parallel. In general when we say 2x and 4x drive strength buffers what exactly it means is that the it could deliver 8 times more current than the normal 1x buffer by employing 8 fingers or even more.

Drastic reduction in resistance

Another advantage of fingering is that resistance reduces drastically by fingering. Let us say you have a resistance of R from the given figure. Now when fingering is done, all these resistances come in parallel hence, the resistance reduces by a factor of N. This is another remarkable advantage of doing fingering,

Subscribe to:

Posts (Atom)

.jpg)

.jpg)