Environment Conditions.

Just like all people on globe does not experience same environment conditions -all transistors on chip does not experience the same environment conditions which influence their functioning.

Voltage and Temperature

These include variation in voltage which is applied to the transistors and temperature at that portion of the transistor.

Width or shape of transistors. (Process)

Different people across the globe are built differently. People in Germany and Russia have their average height different from people in India.

Similar way the transistor may also be on different regions on die and chip. For the same region due to process variation, the width of transistor might be different in in different areas of the chip.

This caused the delay to vary across the different regions on the chip.

We also fix timing across the maximum and minimum operating as operating conditions for the chip to function by taking these as setup and hold corners.

On chip Variation

To address these issues of variation in delay of transistors we basically add delay in transistors by adding a blanket value on each transistor delay to address these variations.

Advanced On Chip Variation

Applying a blanket value of derate would be more pessimistic for your design.

AOCV tries to address two types of variations

1. Random Variation.

As name says random variations are those which cannot be predicted. Like the metal thickness at that region, dioxide thickness , implant doses.

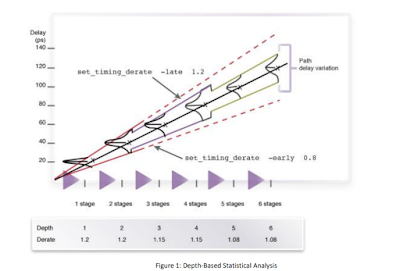

- Random variations are proportional to the depth and they decrease proportionally based on depth.

- For example the if we put in the a pessimism of 10ps derate on a cell for random variation then 8 stages will have around 80ps of

- But 80ps is too pessimistic for the overall path since the overall chance of each cell in the path suffering 10ps derate is less.

- Hence we decide the random variation based on the depth of the cell within the path and reduce it as the depth decreases.

2. Systematic Variation

Systematic variation are based on the distance. They include gate length, gate width and interconnect width etc.

- The more the distance of the devices physically on the die, the more is the derate applied on the device.

- Since the devices on different regions of the die experience PVT differently like temperature across the globe is different regions.